Introduction

For this I am using Quartus II Web Edition 13.0 SP1, which contains Qsys and Nios II EDS. I will initially follow the steps found in [1] up to section 7 where instead I will move to using Nios II Software Build Tools for Eclipse to build and deploy a test application.

System Creation

Create the project in Quartus II, start Qsys, and add the Nios II soft processor, as per [1]. The DE0-Nano, like the DE2-115, uses a 50MHz clock source. You are able to select and use theNios II/s and Nios II/f versions of the processor, however, unless you purchase a license, you will be presented with a dialog window after configuring the FPGA about the time limited OpenIP core. Do not close this window until you are finished or you will not be able to load any applications on the processor.

The remainder of the setup in Qsys is very straight-forward. You may realize that when adding the PIO core for the switches you used a width of 8 bits but the DE0-Nano only contains 4 switches. This is fine – I modified the width down to 4 bits and this did not affect the outcome of the base-end address range assigned by Qsys when using System->Assign Base Addresses (end = base + Fh).

As you prepare to instantiate the Nios II system, [1] suggests to call the parameter for the LEDs LEDG, however the DE0-Nano QSF uses the name LED. You should be able to account for this in Pin Planner but if you want to enter the assignments directly, say using the tcl console, then use the text below which uses LEDG.

set_location_assignment PIN_A15 -to LEDG[0]

set_location_assignment PIN_A13 -to LEDG[1]

set_location_assignment PIN_B13 -to LEDG[2]

set_location_assignment PIN_A11 -to LEDG[3]

set_location_assignment PIN_D1 -to LEDG[4]

set_location_assignment PIN_F3 -to LEDG[5]

set_location_assignment PIN_B1 -to LEDG[6]

set_location_assignment PIN_L3 -to LEDG[7]

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to LEDG[0]

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to LEDG[1]

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to LEDG[2]

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to LEDG[3]

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to LEDG[4]

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to LEDG[5]

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to LEDG[6]

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to LEDG[7]

Top Level Module

You can add the top level file to perform the system instantiation in either Verilog or VHDL as described in [1]. You can copy the Verilog code from the block below. Notice that the input SW is four bits instead of eight. This is because we only have four switches on the DE0-Nano.

module lights (

input CLOCK_50,

input [3:0] SW,

input [0:0] KEY,

output [7:0] LEDG

);

nios_system NiosII (

.clk_clk (CLOCK_50),

.reset_reset_n (KEY),

.switches_export (SW),

.leds_export (LED)

);

endmodule

Also add the .qip file which is generated by Qsys, Project->Add/Remove Files in Project. Browse for the .qip file using the … button in directory lights/synthesis (change the filer in the open file dialog to see IP Variation Files). Once selected, click the Add button and then OK to close the Settings window.

The inputs/outputs will be the physical pins to be setup in the next section.

Pin Assignments

With Pin Planner

First start Analysis & Elaboration (Processing -> Start -> Analysis & Elaboration) and then open the Pin Planner (Assignments -> Pin Planner). Then review the diagram below and make your window look similar.

Manually

You can manually add the pin assignments using the Tcl console window (View -> Utility Windows -> Tcl Console). You may copy the assignments from the code blocks above (for LEDG) and below for KEY[0] and SW[3:0].

set_location_assignment PIN_J15 -to KEY[0]

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to KEY[0]

set_location_assignment PIN_M1 -to SW[0]

set_location_assignment PIN_T8 -to SW[1]

set_location_assignment PIN_B9 -to SW[2]

set_location_assignment PIN_M15 -to SW[3]

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to SW[0]

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to SW[1]

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to SW[2]

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to SW[3]

Timing

When running through the TimeQuest tutorial, [5], I found that I had to add CLOCK_50, set the clock uncertainty, and derive the clock uncertainty after reading the SDC file. All of this can be done through the Constraints menu; see the screen shots below to see what values I used.

Then update the timing netlist and report setup summary. When finished CLOCK_50 has 12.703ns slack, YMMV. Write the SDC file and add the output the project in Quartus II. Below are the relevant entries in the SDC file for CLOCK_50. You may also see similar lines for altera_reserved_tck and the setup of false paths.

create_clock -name {CLOCK_50} -period 20.000 -waveform { 0.000 10.000 } [get_ports {CLOCK_50}]

set_clock_uncertainty -rise_from [get_clocks {CLOCK_50}] -rise_to [get_clocks {CLOCK_50}] 0.020

set_clock_uncertainty -rise_from [get_clocks {CLOCK_50}] -fall_to [get_clocks {CLOCK_50}] 0.020

set_clock_uncertainty -fall_from [get_clocks {CLOCK_50}] -rise_to [get_clocks {CLOCK_50}] 0.020

set_clock_uncertainty -fall_from [get_clocks {CLOCK_50}] -fall_to [get_clocks {CLOCK_50}] 0.020

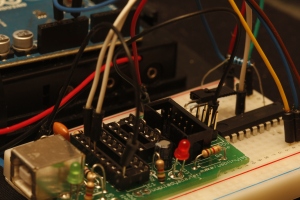

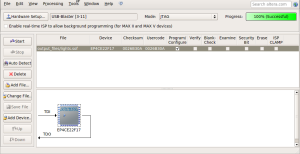

Configuring the FPGA

Start the Quartus II Programmer from Quartus II Tools->Programmer. The programmer may start with everything ready to go, if not follow these steps.

- Press the Hardware Setup… button and select the USB-Blaster

- Press the Auto Detect button

- Highlight the row with the device EP4CE22CF17 and then Edit->Change File; browse for the .SOF file, check in the output_files folder

- Ensure that Program/Configure is selected

- Press the Start button

Testing the System

Start Eclipse for Nios II (Tools->Nios II Software Build Tools for Eclipse). Create a new Nios II Application and BSP from Template. Browse for the SOPC file created by Qsys, the CPU name should be automatically selected. Enter your desired project name and select Blank Template as the Project template. Click the Finish button.

You now have two projects, project_name and project_name_bsp, select project_name, right-click and select new file, and enter a file name. Copy the contents of the block below into the new file and save. You can now run the project as a Nios II hardware and play with the switches to change which LEDs are illuminated.

#include <system.h>

#define switches (volatile char*)SWITCHES_BASE

#define leds (char*)LEDS_BASE

int main()

{

while(1)

{

*leds = ((~(*switches) & 0x0F) << 4) | *switches;

}

return 0;

}

Follow-up

References